經過數十年發展,半導體工藝制程已逐漸逼近亞納米物理極限,傳統硅基集成電路難以依靠進一步縮小晶體管面內尺寸來延續摩爾定律。發展垂直架構的多層互連CMOS邏輯電路以實現三維集成技術的突破,已成為國際半導體領域積極探尋的新方向。在2023年12月美國舊金山召開的國際電子器件會議(IEDM)中,三星、臺積電等半導體公司爭相發布相關研究計劃。

由于硅基晶體管的現代工藝采用單晶硅表面離子注入的方式,難以實現在一層離子注入的單晶硅上方再次生長或轉移單晶硅。雖然可以通過三維空間連接電極、芯粒等方式提高集成度,但是關鍵的晶體管始終被限制在集成電路最底層,無法獲得厚度方向的自由度。新材料或顛覆性原理因此成為備受關注的重要突破點。

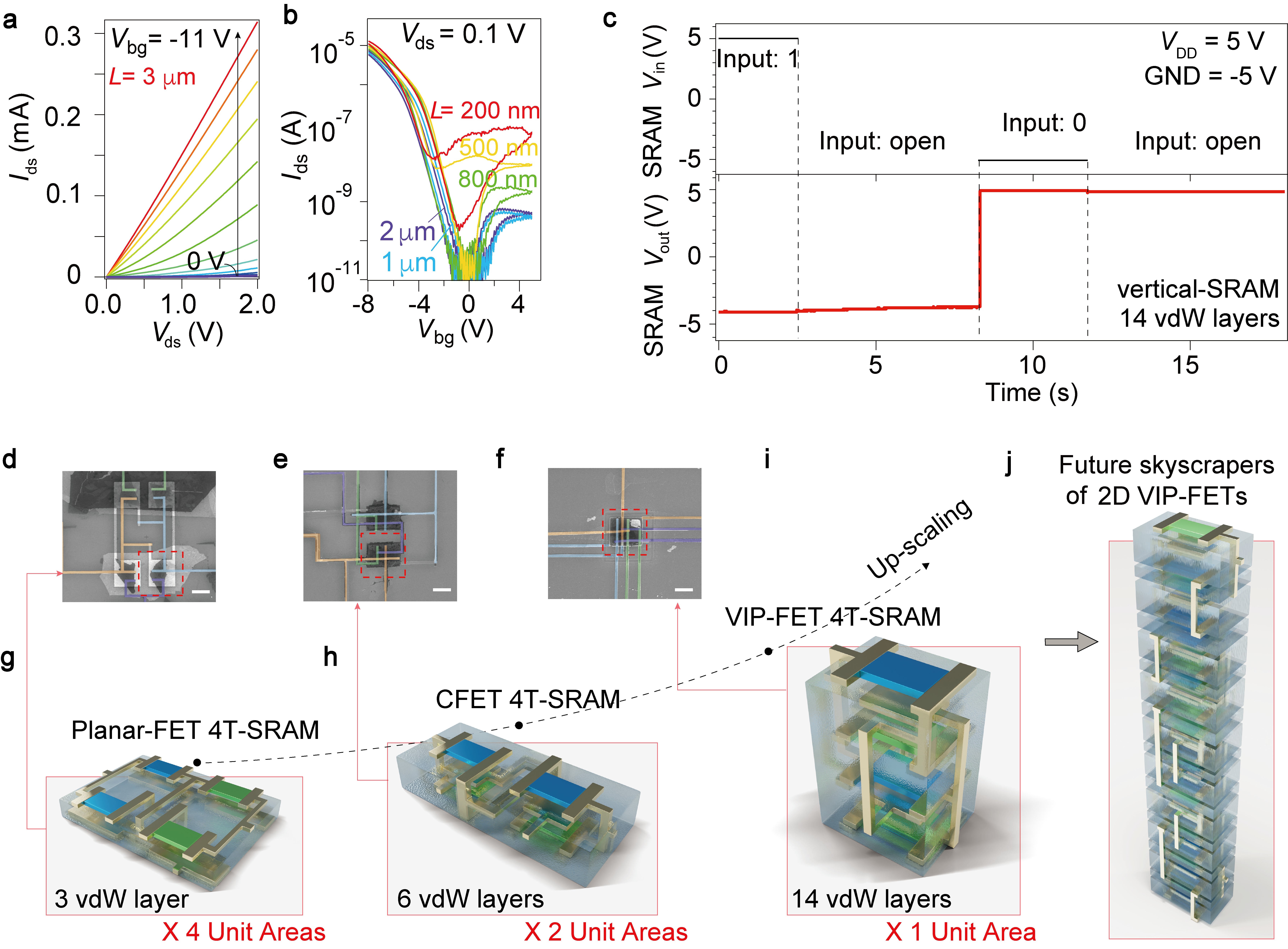

近日,中國科學院大學周武課題組與山西大學韓拯課題組、遼寧材料實驗室王漢文課題組、中山大學候仰龍課題組、中國科學院金屬所李秀艷課題組等合作,提出了一種全新的基于界面耦合的p型摻雜二維半導體方法。該方法采用界面效應的顛覆性路線,工藝簡單、效果穩定,并且可以有效保持二維半導體本征的優異性能。在此基礎上,該研究團隊利用垂直堆疊的方式制備了由14層范德華材料組成、包含4個晶體管的互補型邏輯門NAND以及SRAM等器件(如圖1所示)。這一創新方法打破了硅基邏輯電路的底層“封印”,基于量子效應獲得了三維(3D)垂直集成多層互補型晶體管電路,為后摩爾時代未來二維半導體器件的發展提供了思路。

圖1. 二維半導體垂直3D集成互補型邏輯電路SRAM原型器件的實現

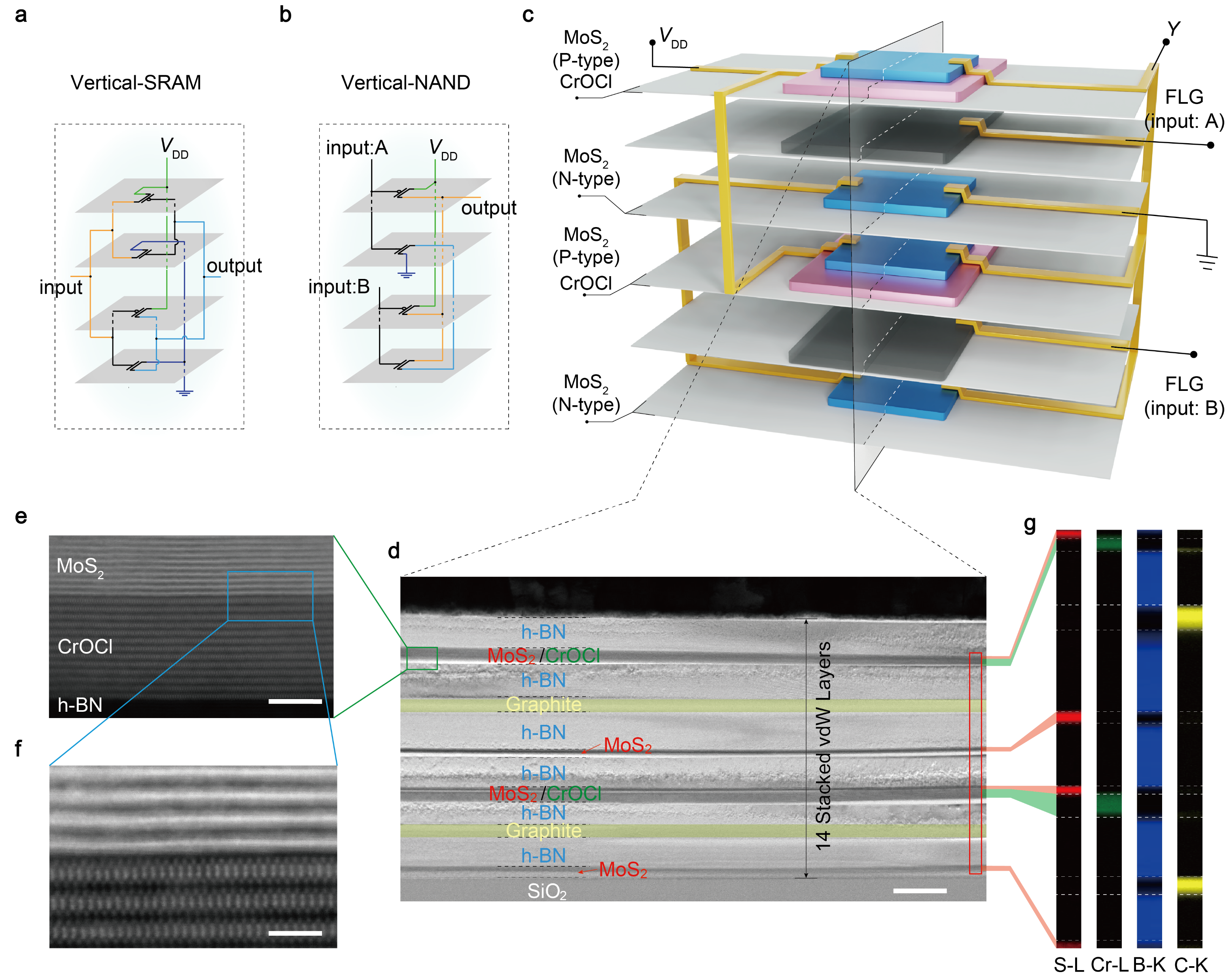

利用低電壓球差校正掃描透射電鏡,該研究團隊對由14層范德華材料組成的NAND器件的截面結構進行了原子尺度的深入表征。分析結果表明,器件關鍵組分MoS2、CrOCl與hBN層之間具有原子級清晰的界面,相應的電子能量損失譜化學成像進一步證實了這一結論(如圖2所示)。密度泛函理論計算揭示了這種界面耦合誘導的極性反轉源于過渡金屬硫族化物(TMD)材料向CrOCl的電荷轉移以及伴隨的電子間相互作用。該摻雜策略預期可廣泛適用于TMD材料與具有高功函數的層狀絕緣體之間的界面,有望推動半導體電路先進三維集成的進一步發展。

圖2. 包含14個范德華材料層的三維集成邏輯電路的原子尺度結構分析

該研究成果以“Van der Waals polarity-engineered 3D integration of 2D complementary logic”為題于2024年5月29日在Nature雜志在線發表。中國科學院金屬所郭藝萌同學、中國科學院金屬所李江旭博士后、山東大學詹學鵬教授、中國科學院大學王春雯同學、上海科技大學李敏同學為論文共同第一作者。中國科學院金屬所李秀艷研究員、中山大學侯仰龍教授、中國科學院大學周武教授、遼寧材料實驗室王漢文副研究員、山西大學韓拯教授為論文的共同通訊作者。北京大學王潤聲教授和王子瑞同學在TCAD仿真方面給予了支持,山西大學張靖教授和秦成兵教授在測試方面給予支持,北京大學葉堉教授為本工作提供了CrOCl晶體和測試的協助,上海科技大學劉健鵬教授為本文DFT計算提供了支撐。該研究得到科技部納米科技重點專項、國家自然科學基金、沈陽材料科學國家研究中心、遼寧材料實驗室、山西大學量子光學與光量子器件國家重點實驗室、北京高校卓越青年科學家計劃項目、中國科學院穩定支持基礎研究領域青年團隊計劃和中國科學院大學電子顯微學實驗室等的資助。

點擊查看視頻:基于量子效應的新原理二維半導體摻雜與三維垂直集成

原文鏈接: https://www.nature.com/articles/s41586-024-07438-5